### **General Description**

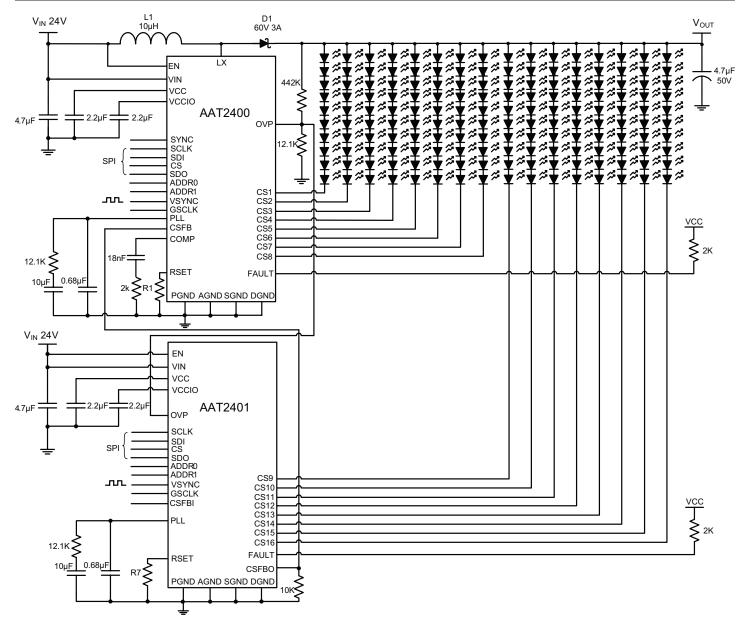

The AAT2400/2401 is a highly integrated, high efficiency white LED backlight solution for large size LCD panels used in LCD TVs. To accommodate power requirements, the solution consists of two devices, a master device (AAT2400) and a slave device (AAT2401). The devices operate from a regulated 24V DC power supply. The master device supplies a 40V rail to drive 10 series LEDs with a typical V<sub>F</sub> of 3.6V. 16 precision current sinks split evenly between the master and slave devices provide constant current drive for up to 160 white LEDs.

A SPI compatible interface operates up to 30MHz, allowing fast, independent digital control of each current sink. Full scale LED current is programmed from 30mA to 100mA using an external resistor. LED brightness variation is compensated by setting relative current sink magnitudes with an 8-Bit Dot Correction register for each LED current sink.

The AAT2400/2401 provides a 12-bit programmable phase delay per LED current sink that can be used to synchronize the LEDs to  $V_{\text{SYNC}}$ . Device addressing provides for up to 256 LED strings. A 12-bit programmable Gray Scale PWM brightness setting is generated via a clock from a PLL synchronized to  $V_{\text{SYNC}}$ , or from the external GSCLK pin.

The AAT2400/2401 provides fault handling and fault reporting through the interface. If LEDs are shorted on one or more strings, the current sinks will maintain operation due to the high voltage rating of the outputs. However, a fault condition will be reported on the open drain Fault pin. Similarly, if an open circuit is detected or an over-temperature condition arises, the fault is reported on the Fault pin. When a fault is reported, the nature of the fault condition can be read through the serial interface.

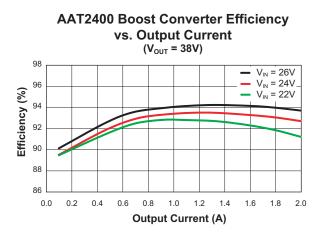

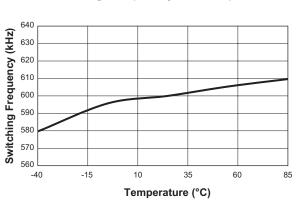

The AAT2400 boost converter provides an output voltage regulated by the string with the highest voltage requirement allowing a wide range of LED characteristics, while maintaining the lowest possible power dissipation. The boost switching frequency is 600kHz to allow for optimum efficiency with the smallest external filter. Alternatively, the device may be synchronized to an external clock. Current mode control provides fast response to line and load transients. Thermal protection circuitry shuts down the boost converter and the current sinks in the event of an over-temperature condition.

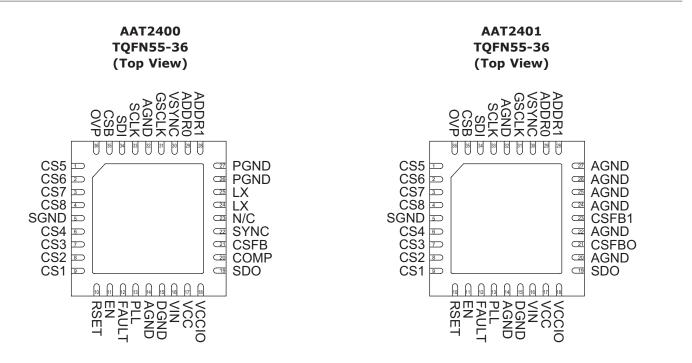

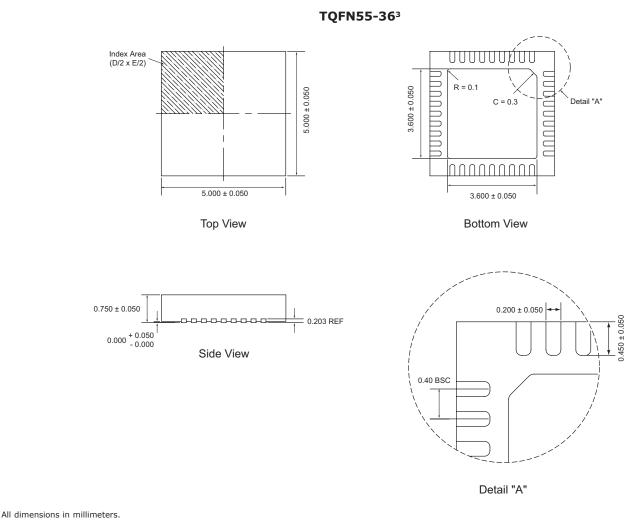

The AAT2400 and AAT2401 are available in Pb-free, thermally enhanced 36-pin 5x5mm TQFN packages.

## Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

#### **Features**

- V<sub>IN</sub> Range: 10.8V 28V

- Integrated Boost Converter

- V<sub>OUT(MAX)</sub>: 40V

- I<sub>OUT(MAX)</sub>: 1.6A

- Up to 95% Efficiency

- Switching Frequency Options

- 600 kHz

- Sync to External Clock (optional)

- 16 LED Current Sinks up to 100mA/ch

- ±2.5% Accuracy (60mA)

- ±2.0% Matching (60mA)

- SPI Interface

- Digitally Programmable Individual Channels

- Up to 30MHz Clock Speed

- Read/Write Registers

- Precision PWM Digital Brightness Control

- 12-bit Individual Gray Scale PWM Brightness

- 12-bit Individual Channel Phase Delay

- 8-bit Individual Current Setting (Dot Correction)

- V<sub>SYNC</sub> Derived Internal Oscillator

- V<sub>SYNC</sub> PWM and Delay Synchronization

- Device Addressing

- 16 Possible Address Settings

- Up to 256 Current Sinks

- Fault Reporting

- Integrated Fault Protection

- Open/Short LED(s)

- Current Limit Protection

- Over-Voltage Protection

- Over-Temperature Protection

- Soft-Start to Minimize Inrush Current

- TQFN55-36 Low Profile Package

- -40°C to +85°C Temperature Range

## Applications

- Large Size LCD TV, Panels

- White LED Backlight

## Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

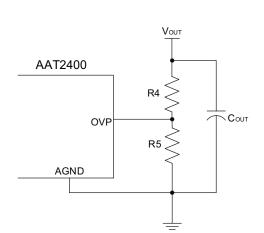

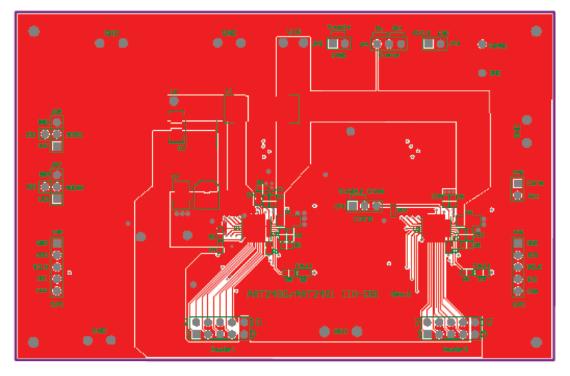

## **Typical Application Circuit**

# DATA SHEET AAT2400/240 |

# Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

## **AAT2400** Pin Descriptions

| Pin #  | Symbol     | Function | Description                                                                                                                                                         |  |

|--------|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1      | CS5        | 0        | Output current sink 5 <sup>1</sup> .                                                                                                                                |  |

| 2      | CS6        | 0        | Output current sink 6 <sup>1</sup> .                                                                                                                                |  |

| 3      | CS7        | 0        | Output current sink 7 <sup>1</sup> .                                                                                                                                |  |

| 4      | CS8        | 0        | Output current sink 8 <sup>1</sup> .                                                                                                                                |  |

| 5      | SGND       | GND      | Current sink ground. Connect to GND as closely as possible to the device.                                                                                           |  |

| 6      | CS4        | 0        | Output current sink 4 <sup>1</sup> .                                                                                                                                |  |

| 7      | CS4<br>CS3 | 0        | Output current sink 3 <sup>1</sup> .                                                                                                                                |  |

| 8      | CS2        | 0        | Output current sink 2 <sup>1</sup> .                                                                                                                                |  |

| 9      | CS2<br>CS1 | 0        |                                                                                                                                                                     |  |

| 9      | C51        | 0        | Output current sink 1 <sup>1</sup> .                                                                                                                                |  |

| 10     | RSET       | I        | Resistor for setting maximum current sink DC level. Connect a resistor between this pin and AGND pin.                                                               |  |

| 11     | EN         | Ι        | Logic high enable pin. Apply a logic high voltage after power is applied to VIN or connect to VIN through a RC time delay network to enable the device.             |  |

| 12     | FAULT      | 0        | Open drain fault signal. Pull up to logic supply with external resistor.                                                                                            |  |

| 13     | PLL        | I/O      | PLL compensation. Connect associated network between this pin and AGND.                                                                                             |  |

| 14, 32 | AGND       | GND      | Analog ground. Connect to GND with one single connection.                                                                                                           |  |

| 15     | DGND       | GND      | Digital ground. Connect to GND as closely as possible to the device.                                                                                                |  |

| 16     | VIN        | I        | IC and boost converter power supply.                                                                                                                                |  |

| 17     | VCC        | I/O      | Internally regulated power supply. Decouple with 2.2µF/6.3V capacitor to AGND.                                                                                      |  |

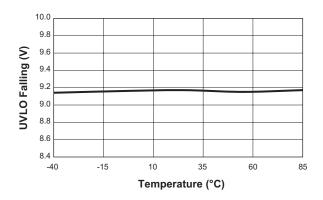

| 18     | VCCIO      | I/O      | Internally regulated power supply (3.3V) for SDO. Decouple with 2.2µF/6.3V capacitor to DGND.                                                                       |  |

| 19     | SDO        | 0        | SPI interface serial data output.                                                                                                                                   |  |

| 20     | COMP       | I        | Boost converter compensation. Connect external resistor and capacitor to this pin and AGND.                                                                         |  |

| 21     | CSFB       | I        | Current sink feedback. Connect to slave device CSFBO with a $10k\Omega$ pull-down resistor.                                                                         |  |

| 22     | SYNC       | I        | Connect to an external clock for synchronization Connect to PGND if not used.                                                                                       |  |

| 23     | N/C        |          | No connect                                                                                                                                                          |  |

| 24, 25 | LX         | 0        | Switching node of boost converter. Connect a $10\mu$ H inductor between this pin and VIN. Connect a Schottky diode between this pin and the boost output capacitor. |  |

| 26, 27 | PGND       | GND      | Power ground of boost converter integrated NMOS switching device. Boost output capacitor must be placed very close to this pin.                                     |  |

| 28     | ADDR1      | I        | MSB device address. Connect to VCC, GND, SDI or leave unconnected to set address.                                                                                   |  |

| 29     | ADDR0      | I        | LSB device address. Connect to VCC, GND, SDI or leave unconnected to set address.                                                                                   |  |

| 30     | VSYNC      | I        | Vertical sync. PWM operation synchronization and reset.                                                                                                             |  |

| 31     | GSCLK      | I        | PWM clock. Apply clock or connect to GND if not used.                                                                                                               |  |

| 33     | SCLK       | I        | SPI interface serial clock.                                                                                                                                         |  |

| 34     | SDI        | I        | SPI interface serial data input.                                                                                                                                    |  |

| 35     | CSB        | I        | SPI interface active low chip select.                                                                                                                               |  |

| 36     | OVP        | I        | Over-voltage protection pin. Connect resistive divider between VOUT and GND.                                                                                        |  |

| EP     | 001        | 1        | Exposed paddle. Connect to PCB GND plane. PCB paddle heat sinking should maintain accept-<br>able junction temperature.                                             |  |

1. Unused current sink channels must be terminated. Refer to the Channel Disable paragraph in the Application Information section of this datasheet.

# DATA SHEET AAT2400/240 |

# Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

## **AAT2401** Pin Descriptions

| Pin #                     | Symbol | Function | Description                                                                                                                                                  |  |  |

|---------------------------|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1                         | CS5    | 0        | Output current sink 5 <sup>1</sup> .                                                                                                                         |  |  |

| 2                         | CS6    | 0        | Output current sink 6 <sup>1</sup> .                                                                                                                         |  |  |

| 3                         | CS7    | 0        | Output current sink 7 <sup>1</sup> .                                                                                                                         |  |  |

| 4                         | CS8    | 0        | Output current sink 8 <sup>1</sup> .                                                                                                                         |  |  |

| 5                         | SGND   | GND      | Current sink ground. Connect to GND as closely as possible to the device.                                                                                    |  |  |

| 6                         | CS4    | 0        | Output current sink 4 <sup>1</sup> .                                                                                                                         |  |  |

| 7                         | CS3    | 0        | Output current sink 3 <sup>1</sup> .                                                                                                                         |  |  |

| 8                         | CS2    | 0        | Output current sink 2 <sup>1</sup> .                                                                                                                         |  |  |

| 9                         | CS1    | 0        | Output current sink 1 <sup>1</sup> .                                                                                                                         |  |  |

| 10                        | RSET   | I        | Resistor for setting maximum current sink DC level. Connect a resistor between this pin<br>and AGND pin.                                                     |  |  |

| 11                        | EN     | I        | Logic high enable pin. Apply a logic high voltage after power is applied to the VIN. Or connect to VIN through a RC time delay network to enable the device. |  |  |

| 12                        | FAULT  | 0        | Open drain fault signal. Pull up to logic supply with external resistor.                                                                                     |  |  |

| 13                        | PLL    | I/O      | PLL compensation. Connect associated network between this pin and AGND.                                                                                      |  |  |

| 14, 32                    | AGND   | GND      | Analog ground. Connect to GND with one single connection.                                                                                                    |  |  |

| 15                        | DGND   | GND      | Digital ground. Connect to GND as closely as possible to the device.                                                                                         |  |  |

| 16                        | VIN    | I        | IC and boost converter power supply.                                                                                                                         |  |  |

| 17                        | VCC    | I/O      | Internally regulated power supply. Decouple with 2.2µF/6.3V capacitor to AGND.                                                                               |  |  |

| 18                        | VCCIO  | I/O      | Internally regulated power supply (3.3V) for SDO. Decouple with $2.2\mu$ F/6.3V capacitor to DGND.                                                           |  |  |

| 19                        | SDO    | 0        | SPI interface serial data output.                                                                                                                            |  |  |

| 20, 22, 24,<br>25, 26, 27 | AGND   | GND      | Connect to GND with one single connection.                                                                                                                   |  |  |

| 21                        | CSFBO  | 0        | Current sink feedback output. Connect to master device CSFB with a $10 k \Omega$ pull-down resistor                                                          |  |  |

| 23                        | CSFBI  | I        | Current sense feedback input. Connect to VCC if not used.                                                                                                    |  |  |

| 28                        | ADDR1  | I        | MSB device address. Connect to VCC, GND, SDI or leave unconnected to set address.                                                                            |  |  |

| 29                        | ADDR0  | I        | LSB device address. Connect to VCC, GND, SDI or leave unconnected to set address.                                                                            |  |  |

| 30                        | VSYNC  | I        | Vertical sync. PWM operation synchronization and reset.                                                                                                      |  |  |

| 31                        | GSCLK  | I        | PWM clock. Apply clock or connect to GND if not used.                                                                                                        |  |  |

| 33                        | SCLK   | I        | SPI interface serial clock.                                                                                                                                  |  |  |

| 34                        | SDI    | I        | SPI interface serial data input.                                                                                                                             |  |  |

| 35                        | CSB    | I        | SPI interface active low chip select.                                                                                                                        |  |  |

| 36                        | OVP    | I        | Over-voltage protection pin. Connect resistive divider between VOUT and GND.                                                                                 |  |  |

| EP                        |        |          | Exposed paddle. Connect to PCB GND plane. PCB paddle heat sinking should maintain acceptable junction temperature.                                           |  |  |

1. Unused current sink channels must be terminated. Refer to the Channel Disable paragraph in the Application Information section of this datasheet.

## Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

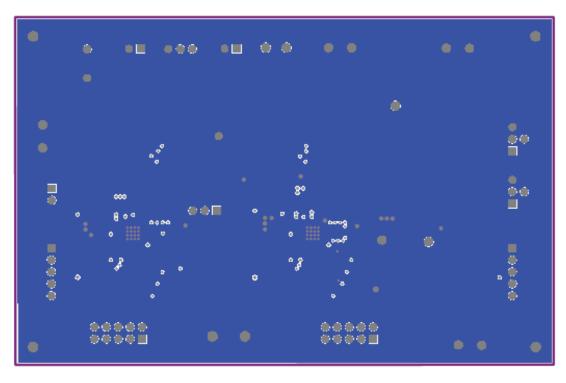

### **Pin Configuration**

### Absolute Maximum Ratings<sup>1</sup>

$T_A = 25^{\circ}C$  unless otherwise noted.

| Symbol                                                                                                        | Description                                                                                                                  | Value                       | Units |

|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------|

| V <sub>LX</sub>                                                                                               | LX Voltage to GND                                                                                                            | 45                          |       |

| V <sub>IN,EN</sub>                                                                                            | Input Voltage, EN to GND                                                                                                     | -0.3 to 30                  |       |

| V <sub>CSx</sub>                                                                                              | Output current sinks CS1 – CS16 to GND                                                                                       | -0.3 to 35                  |       |

| V <sub>cc</sub>                                                                                               | Low Voltage Pin to GND                                                                                                       | -0.3 to 6.0                 | V     |

| OVP, COMP, SYNC, VSYNC, GSCLK, RSET,<br>SDI, SDO, SCLK, CS B, PLL, FLAUT,<br>CSFB, CSFBi, CSFBo, ADDR0, ADDR1 | OVP, COMP, SYNC, VSYNC, GSCLK, RSET, SDI, SDO,<br>SCLK, CS B, PLL, FLAUT, CSFB, CSFBi, CSFBo, ADDR0,<br>ADDR1 Voltage to GND | -0.3 to V $_{\rm CC}$ + 0.3 |       |

| I <sub>OUT</sub>                                                                                              | Maximum DC Output Current <sup>2</sup>                                                                                       | 1800                        | mA    |

| T <sub>J</sub>                                                                                                | Maximum Junction Operating temperature                                                                                       | -40 to +150                 | ۰C    |

| T <sub>LEAD</sub>                                                                                             | Maximum Soldering Temperature (at leads, 10 sec)                                                                             | 300                         |       |

## **Thermal Information<sup>3</sup>**

| Symbol        | Description                     | Value | Units |

|---------------|---------------------------------|-------|-------|

| $\Theta_{JA}$ | Thermal Resistance <sup>₄</sup> | 23    | °C/W  |

| PD            | Maximum Power Dissipation       | 4.3   | W     |

1. Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum Rating should be applied at any one time.

2. Based on long-term current density limitation.

3. Mounted on an FR4 board.

4. Derate 23mW/°C above 25°C.

# Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

## **Electrical Characteristics**<sup>1</sup>

$V_{IN}=24V;\ C_{IN}=4.7\mu\text{F},\ C_{OUT}=4.7\mu\text{F};\ C_{VCC}=2.2\mu\text{F};\ L_1=10\mu\text{H};\ R_{SET}=10.2k\Omega\ (I_{CSx}=60\text{mA});\ T_A=-40^\circ\text{C}\ to\ 85^\circ\text{C}\ unless$  otherwise noted. Typical values are at  $T_A=25^\circ\text{C}.$

| Symbol                                  | Description                                  | Conditions                                                             | Min           | Тур  | Max  | Units |

|-----------------------------------------|----------------------------------------------|------------------------------------------------------------------------|---------------|------|------|-------|

| Power Supp                              | ly, Current Sinks                            |                                                                        |               |      |      |       |

| V <sub>IN</sub>                         | Input Voltage Range                          |                                                                        | 10.8          |      | 28.0 | V     |

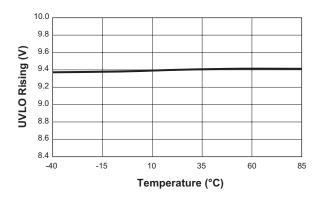

|                                         |                                              | V <sub>IN</sub> Rising                                                 |               |      | 10   | V     |

| V <sub>UVLO</sub>                       | Under-Voltage Threshold                      | Hysteresis                                                             |               | 500  |      | mV    |

|                                         |                                              | $V_{IN}$ Falling                                                       | 8.5           |      |      | V     |

| V <sub>OUT</sub>                        | Output Voltage Range                         | $V_{IN} = 10.8$ to 28.0V                                               | $V_{IN} + 3V$ |      | 40   | V     |

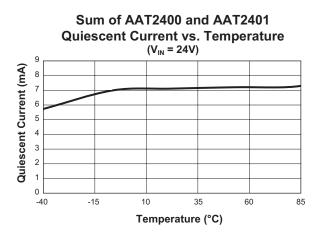

| $\mathrm{I}_{\mathrm{Q}\_2400}$         | Quiescent Current of AAT2400 (no switching)  | $I_{CSx} = 0mA, V_{CSx} = 1V$                                          |               | 3    |      | mA    |

| $I_{Q_{2401}}$                          | Quiescent Current of AAT2401                 | $I_{CSx} = 0mA$ , $V_{CSx} = 1V$                                       |               | 5    |      | mA    |

| $\mathbf{I}_{SD}$                       | VIN Pin Shutdown Current                     | CSn = IN, EN = Logic Low; includes CSx<br>+ LX leakage current         |               | 25   |      | μA    |

| $I_{\text{EN}\_\text{LEAKAGE}}$         | Enable Leakage Current                       | EN = 5V                                                                |               |      | 5    | μA    |

| $I_{\text{ADDR0}}$ , $I_{\text{ADDR1}}$ | Input Current to ADDR0 and ADDR1             | ADDR0 = 5V, ADDR1 = 5V                                                 |               |      | 100  | μA    |

| VOVP                                    | Over-Voltage Threshold                       | V <sub>OUT</sub> Rising                                                | 1.1           | 1.2  | 1.3  | V     |

| VOVP                                    | Over-Voltage Hysteresis                      | V <sub>out</sub> Falling                                               |               | 100  |      | mV    |

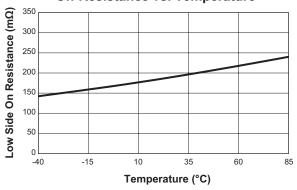

| R <sub>DS(ON)LO</sub>                   | Low Side Switch On-Resistance                |                                                                        |               | 180  |      | mΩ    |

| $I_{\text{LIMIT}}$                      | Low Side Switch Current Limit                |                                                                        | 4.5           |      | 6.5  | A     |

| Fosc                                    | Oscillator Frequency                         |                                                                        | 500           | 600  | 700  | kHz   |

| F <sub>SYNC</sub>                       | Sync Frequency                               |                                                                        | 300           |      | 900  | kHz   |

| T <sub>ss</sub>                         | Soft-Start                                   | $V_{OUT} = 35V$                                                        |               | 1    |      | ms    |

| $\rm I_{CSx}$ / $\rm I_{RSET}$          | Current Set Ratio                            | $I_{CSx}/I_{RSET}$ , $V_{RSET}$ = 0.6V nom, Full Scale Dot Correction  |               | 1024 |      | A/A   |

| $V_{Cx}$                                | Current Sink Voltage                         | EN = Logic High, $I_{CSx}$ = 60mA (R <sub>SET</sub> = 10.2k $\Omega$ ) |               | 0.8  |      | V     |

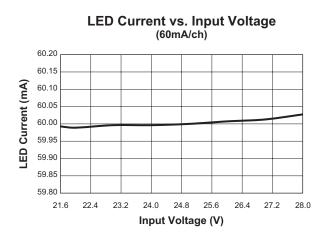

| I <sub>CSx</sub>                        | Current Sink Accuracy                        | I <sub>CSx</sub> = 60mA                                                | -2.5          |      | +2.5 | %     |

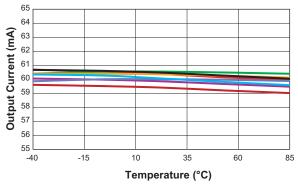

| $I_{\text{CSx-Matching}}$               | Current Matching Between Any Sink<br>Channel | I <sub>CSx</sub> = 60mA                                                | -2            |      | +2   | %     |

| $V_{\text{Cx(SHORT)}}$                  | Shorted Diode(s) Detection Threshold         | I <sub>CSx</sub> = 60mA                                                |               | 3V   |      |       |

| Logic Level                             | Inputs: EN, SYNC, VSYNC, GSCLK, SD           | I, SCLK, CSB                                                           |               |      |      |       |

| V <sub>I(L)</sub>                       | Input Logic Threshold Low                    |                                                                        |               |      | 0.4  | V     |

| V <sub>I(H)</sub>                       | Input Logic Threshold High                   |                                                                        | 1.4           |      |      | V     |

| $V_{I(H)_{EN}}$                         | Enable Logic Threshold High                  |                                                                        | 2.5           |      |      | V     |

# Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

## **Electrical Characteristics**<sup>1</sup>

$V_{IN}=24V;\ C_{IN}=4.7\mu\text{F},\ C_{OUT}=4.7\mu\text{F};\ C_{VCC}=2.2\mu\text{F};\ L_1=4.2\mu\text{H};\ R_{SET}=10.2k\Omega\ (I_{CSx}=60\text{mA});\ T_A=-40^\circ\text{C}\ to\ 85^\circ\text{C}\ unless otherwise\ noted.$  Typical values are at  $T_A=25^\circ\text{C}.$

| Symbol                       | Description                                | Conditions                             | Min  | Тур | Max  | Units |

|------------------------------|--------------------------------------------|----------------------------------------|------|-----|------|-------|

| Logic Level                  | Outputs: SDO, FAULT                        | ·                                      |      |     |      |       |

| VCCIO                        | VCC I/O Voltage Range                      | No Load                                | 2.97 | 3.3 | 3.63 | V     |

| V <sub>O(H)</sub>            | Output Logic Level High                    | $I_{SOURCE} = 4mA, V_{CCIO} = 3.3V$    | 2.4  |     |      | V     |

| V <sub>O(L)</sub>            | Output Logic Level Low                     | $I_{SINK} = -4mA$                      |      |     | 0.4  | V     |

| V <sub>FAULTLOW</sub>        | FAULT Logic Output Low                     |                                        |      |     | 0.4  | V     |

| I <sub>SINK</sub>            | FAULT Logic Hi Leakage                     | $V_{FAULT} = 5.5V$                     |      |     | 1    | μA    |

| Interface: V                 | SYNC, GSCLK                                |                                        |      |     |      |       |

| F <sub>VSYNC</sub>           | VSYNC Maximum Frequency                    |                                        | 55   |     | 250  | Hz    |

| F <sub>GSCLK</sub>           | GSCLK Frequency                            |                                        |      | 1   |      | MHz   |

| t <sub>SETUP(SU_VS)</sub>    | Minimum VSYNC Setup Time                   | GSCLK, VSYNC                           |      | 24  |      | ns    |

| t <sub>HOLD(H_VS)</sub>      | Minimum VSYNC Hold Time                    | GSCLK, VSYNC                           |      | 24  |      | ns    |

| T <sub>GS(HI/LO_MIN)</sub>   | Minimum GSCLK Clock High/Low Time          |                                        |      | 32  |      | ns    |

| t <sub>SCLK(HI/LO_MIN)</sub> | Minimum SCLK Clock High/Low Time           |                                        |      | 32  |      | ns    |

| t <sub>vs(HI/LO_MIN)</sub>   | Minimum VSYNC Clock High/Low Time          |                                        |      | 32  |      | ns    |

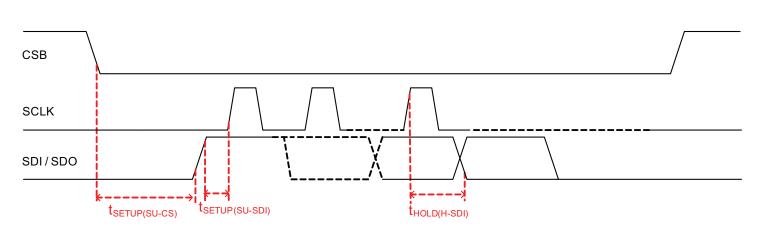

| SPI Interfac                 | ce: SDI, SDO, SCLK, CSB                    |                                        |      |     |      |       |

| F <sub>MAX</sub>             | Maximum Clock Frequency                    |                                        |      | 30  |      | MHz   |

| t <sub>SETUP(SU_SDI)</sub>   | Minimum SDI Setup Time                     | SDI, SCLK                              |      | 24  |      | ns    |

| t <sub>SETUP(SU_CS)</sub>    | Minimum CSB Setup Time                     | CSB, SDI                               |      | 24  |      | ns    |

| t <sub>HOLD(H_SDI)</sub>     | Minimum SDI Hold Time                      | SDI, SCLK                              |      | 24  |      | ns    |

| Thermal Pro                  | otection                                   |                                        |      | ·   |      |       |

| T <sub>J2(SD)</sub>          | T <sub>J</sub> Thermal Shutdown Threshold  | Reset Thermal Threshold                |      | 140 |      | °C    |

| T <sub>J2(HYS)</sub>         | T <sub>J</sub> Thermal Shutdown Hysteresis | CTL1 and CTL2 Registers are Reset to 0 |      | 15  |      | °C    |

| T <sub>J1(SD)</sub>          | T <sub>1</sub> Thermal Warning Threshold   | Warning Thermal Threshold              |      | 120 |      | °C    |

| T <sub>J1(HYS)</sub>         | T <sub>J</sub> Thermal Warning Hysteresis  |                                        |      | 15  |      | °C    |

# Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

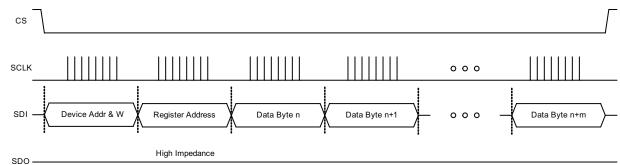

## **SPI Timing Diagram**

# Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

### **Typical Characteristics**

Sum of AAT2400 and AAT2401 Shutdown Current vs. Temperature  $(V_{IN} = 24V)$ 40 Shutdown Current (µA) 35 30 25 20 15 10 5 0 -40 -15 10 35 60 85 Temperature (°C)

> AAT2400 Boost Converter Low Side On-Resistance vs. Temperature

# Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

## **Typical Characteristics**

#### Switching Frequency vs. Temperature

Time (1ms/div)

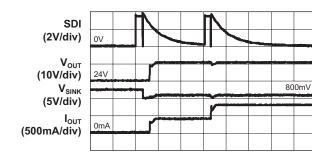

Turn On (V<sub>IN</sub> = 24V; 50mA/ch)

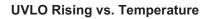

**UVLO Falling vs. Temperature**

# Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

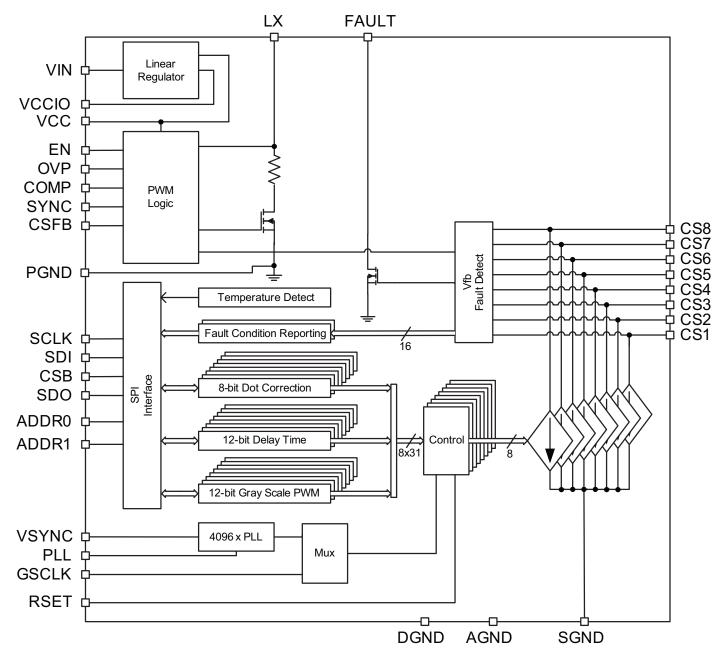

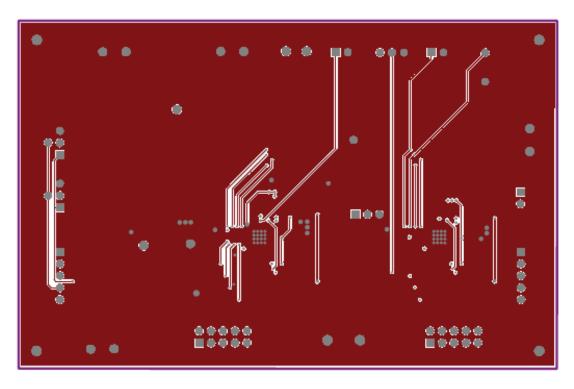

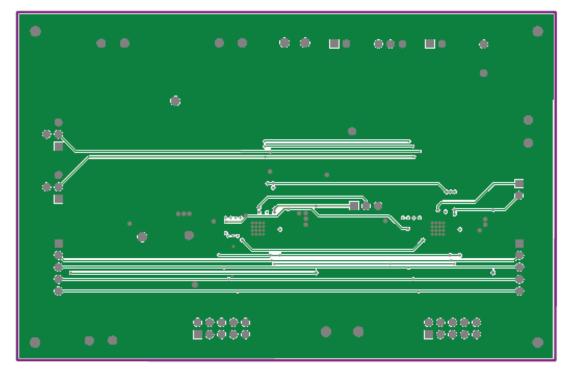

## **Functional Block Diagram**

### AAT2400 (master)

# Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

#### FAULT ↓ CSFBO Linear VIN 🖞 Regulator VCCIO **CSFBI** VCC CS16 **CS15** Vfb Fault Detect ΕN 亡 **CS14** OVP CS13 Ċ **CS12** Temperature Detect 中 CS11 中 CS11 中 CS10 中 CS9 Fault Condition Reporting SCLK 16 SDI CSB SPI Interface 8-bit Dot Correction SDO ADDR0 Control 12-bit Delay Time ADDR1 I 8x31 ՊՈ 12-bit Gray Scale PWM VSYNC 4096 x PLL Mux PLL GSCLK RSET -0-DGND AGND SGND

### AAT2401 (slave)

## **Functional Description**

The AAT2400 consists of a high efficiency DC/DC boost controller, an integrated slew rate controlled input disconnect MOSFET switch, and a MOSFET power switch. A high voltage rectifier, power inductor, output capacitor, feedback compensation network, and OVP resistor divider network are required to implement a DC/DC boost converter.

The AAT2400's boost controller is designed to deliver 1600mA up to 40V. It can drive a total of 16 current regulated sinks (8 from its own and 8 from AAT2401) with 10 HB white LEDs connected in series at each channel.

The maximum LED sink current can be set by an external resistor. Each current sink can be programmed through the SPI interface. Each sink allows independent control with different registers (DOT correction, Gray Scale, Delay, On/Off control configuration).

AAT2400 and AAT2401 both provide one linear regulator for VCCIO supply.

### **Control Loop**

The AAT2400 provides the benefits of current mode control with a simple feedback loop. The device maintains exceptional DC regulation, transient response, and cycleby-cycle current limit with additional RC compensation components. The AAT2400 modulates the power MOSFET switching current in response to changes in output voltage (LED voltage). This allows the voltage loop to directly program the required inductor current in response to changes in the output load. The switching cycle initiates when the N-channel MOSFET is turned ON and current ramps up in the inductor. The ON interval is terminated when the feedback signal crossover the falling edge of the saw wave from the PWM modulator. During the OFF interval, the inductor discharges the energy (inductor ramps down) until the lower threshold, or zero inductor current, is reached. The lower current is equal to the peak current minus a preset hysteresis threshold which determines the inductor ripple current. The peak current is adjusted by the controller until the output current requirement is met. The magnitude of the feedback error signal determines the average input current. Therefore, the AAT2400 controller implements a programmed current source connected to the output capacitor and load resistor. There is no right-half plane zero, and loop stability is achieved with simple RC compensation components.

# Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

## Soft Start / Enable

The input disconnect switch is activated when a valid supply voltage is present and the EN/SET pin is strobed high. Slew rate control on the input disconnect switch ensures minimal inrush current as the output voltage is charged to the input voltage, prior to switching of the N-channel power MOSFET. A monotonic turn-on is guaranteed by the built-in soft-start circuitry, which eliminates output current overshoot across the full input voltage range and over all load conditions.

#### Current Limit and Over-Temperature Protection

The switching of the N-channel MOSFET terminates when a current limit of 6.5A (max) is exceeded. This minimizes power dissipation and component stresses under overload and short-circuit conditions. Switching resumes when the current decays below the current limit. Thermal protection disables the AAT2400/AAT2401 when the internal power dissipation causes the junction temperature to reach the thermal limit threshold (140°C, nominal). When the thermal threshold is reached, the control register, CTL1 or CTL2, is reset to 00h and all current sinks are disabled. When the AAT2400's thermal threshold is reached, the boost converter is also disabled.

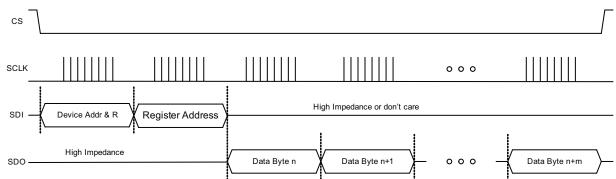

### **Over-Voltage Protection**

Over-voltage protection prevents damage to the AAT2400 during open-circuit on any LED channel sinks causing high output voltage conditions. An over-voltage event is defined as a condition where the voltage on the OVP pin exceeds the over-voltage threshold limit ( $V_{OVP} = 1.2V$  typical). When the voltage on the OVP pin has reached the threshold limit, the converter stops switching and the output voltage decays. Switching resumes when the voltage on the OVP pin drops below the lower hysteresis limit, maintaining an average output voltage between the upper and lower OVP thresholds multiplied by the resistor divider scaling factor.

### **Under-Voltage Lockout**

Internal bias of all circuits is controlled via the V<sub>IN</sub> input. Under-voltage lockout (UVLO) guarantees sufficient VIN bias and proper operation of all internal circuitry prior to soft start.

### **Current Sink Control**

Each current sink has an independent property programmed by the following registers. The AAT2400 contains current sinks 1 through 8. The AAT2401 contains current sinks 9 through 16.

#### **Dot Correction**

Each current sink can have a separate current setting to compensate for relative LED brightness. This register has a default setting of half scale.

| ADDR:<br>00h to 1Eh |          | DOTn:<br>DOT Correction Current Setting |        |                |  |

|---------------------|----------|-----------------------------------------|--------|----------------|--|

| Bit                 | Bit Name | Default                                 | Access | Description    |  |

| 7:0                 | DOTn 7:0 | 7Fh                                     | R/W    | 8-bit DOT word |  |

Table 1: DOT Correction Current Setting.

#### **Gray Scale**

Each current sink has a unique PWM duty cycle setting to provide a given brightness. The gray scale register is a 12-bit word divided into an 8-bit word and a 4-bit word. This register has a default setting of  $\frac{1}{2}$  scale, or 0400h. Only even register addresses are used starting from 40h to 7Eh.

|     | ADDR:<br>h to 7Eh | GSn LSB:<br>Gray Scale Setting LSB |        |                             |

|-----|-------------------|------------------------------------|--------|-----------------------------|

| Bit | Bit Name          | Default                            | Access | Description                 |

| 7:0 | GSn 7:0           | 00h                                | R/W    | 8 LSBs of 12-bit<br>GS word |

Table 2: Gray Scale Setting LSB.

| ADDR:<br>40h to 7Eh |          | GSn MSB:<br>Gray Scale Setting MSB |        |                             |

|---------------------|----------|------------------------------------|--------|-----------------------------|

| Bit                 | Bit Name | Default                            | Access | Description                 |

| 3:0                 | GSn 11:8 | 04h                                | R/W    | 4 MSBs of 12-bit<br>GS word |

Table 3: Gray Scale Setting MSB.

### Delay

Each current sink has a unique delay time from the start of  $V_{\text{SYNC}}$  to when the current sink PWM cycle begins. The delay register is a 12-bit word divided into an 8-bit word

# Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

and a 4-bit word. This register has a default setting of 0. Only even register addresses are used. Starting from 80h, every other even register is programmed up to BEh.

| ADDR:<br>80h to BEh |          | DLYn LSB:<br>Delay Setting LSB |        |                             |

|---------------------|----------|--------------------------------|--------|-----------------------------|

| Bit                 | Bit Name | Default                        | Access | Description                 |

| 7:0                 | DLYn 7:0 | 00h                            | R/W    | 8 LSBs of 12-bit<br>GS word |

#### Table 4: Delay Setting LSB.

| ADDR:<br>80h to BEh |           | DLYn MSB:<br>Delay Setting MSB |        |                              |

|---------------------|-----------|--------------------------------|--------|------------------------------|

| Bit                 | Bit Name  | Default                        | Access | Description                  |

| 3:0                 | DLYn 11:8 | 00h                            | R/W    | 4 MSBs of 12-<br>bit GS word |

#### Table 5: Delay Setting MSB.

#### **Current Sink ON/OFF**

Each current sink can be independently enabled or disabled. In the event of an over temperature condition, this register is reset to 00h and must be reprogrammed to resume operation. It has a default setting of 00h (all sinks are off).

| ADI | DR: C0h      | CTL1:<br>This Register Enables or<br>Disables Each Current Sink<br>Independently |        |                                                |

|-----|--------------|----------------------------------------------------------------------------------|--------|------------------------------------------------|

| Bit | Bit Bit Name |                                                                                  | Access | Description                                    |

| 7:0 | CS8:CS1      | 00h                                                                              | R/W    | 0 = current<br>sink OFF, 1=<br>current sink ON |

#### Table 6: CTL1 Setting.

| AD  | DR: C2h  | CTL2:<br>This Register Enables or<br>Disables Each Current Sink<br>Independently |        |                                                |  |

|-----|----------|----------------------------------------------------------------------------------|--------|------------------------------------------------|--|

| Bit | Bit Name | Default                                                                          | Access | Description                                    |  |

| 7:0 | CS16:CS9 | 00h                                                                              | R/W    | 0 = current sink<br>OFF, 1= current<br>sink ON |  |

#### Table 7: CTL2 Setting.

# Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

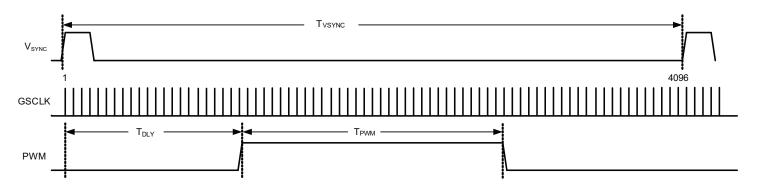

timing diagram). If  $T_{\text{PWM}}$  is not met by the end of  $T_{\text{VSYNC}}$ , the PWM on time will overflow onto the next  $T_{\text{VSYNC}}$  period. LED % Brightness =  $T_{\text{PWM}}$  /4096 x 100.

### Device Address Setup

The device address is set by the two address pins, ADDR1 and ADDR0. Each address pin has four decode levels resulting in 16 possible address settings. The address is programmed by connecting ADDR1 and ADDR0 to VCC, GND, SDI, or by leaving the ADDR pin unconnected. The master and slave devices can be programmed with the same device address. The register addressing will automatically select the appropriate master/slave device for the addressed current sink.

**PWM Timing**

The PWM "on time" of a given current sink is set by the

gray scale and delay registers according to the following timing diagram.  $T_{VSYNC}$  is the period of the  $V_{SYNC}$  signal,

typically 1/120 Hz, or 8 1/3 ms, but  $T_{\rm VSYNC}$  can be as short as 500 $\mu s.$  GSCLK is either derived from  $V_{\rm SYNC}$ , where  $F_{\rm GSCLK}$

= 4096 x  $F_{VSYNC}$ , or supplied by an external signal at the

GSCLK pin. T<sub>DLY</sub> is the number between 0 and 4095 of the

DLY register, and is the number of GSCLK rising edges

between the rising edge of  $V_{SYNC}$  and the rising edge of the

PWM signal. Likewise,  $T_{PWM}$  is the number between 0 and

4095 of the GS register, and is the number of GSCLK

periods of the PWM "on time". The current sink conducts

during the PWM "on time" (shown high in the following

Figure 1: PWM Timing Diagram.

| Dev | ice Address | SPI Address:<br>Addr1 Addr0 Decoding of Address Set Resistors        |

|-----|-------------|----------------------------------------------------------------------|

| Bit | Bit Name    | Description                                                          |

| 1:0 | ADDR0       | 00: connect to VCC; 01: OPEN; 10: connect to SDI; 11: connect to GND |

| 3:2 | ADDR1       | 00: connect to VCC; 01: OPEN; 10: connect to SDI; 11: connect to GND |

Table 8: Device Address Settings.

# DATA SHEET AAT2400/240 I

## Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

| Config | uration |   | Bits |   |   |   |   |   |   |               |

|--------|---------|---|------|---|---|---|---|---|---|---------------|

| ADDR1  | ADDR0   | 6 | 5    | 4 | 3 | 2 | 1 | 0 | W | Address (Hex) |

| VCC    | VCC     | 1 | 0    | 1 | 0 | 0 | 0 | 0 | 0 | A0            |

| VCC    | OPEN    | 1 | 0    | 1 | 0 | 0 | 0 | 1 | 0 | A2            |

| VCC    | SDI     | 1 | 0    | 1 | 0 | 0 | 1 | 0 | 0 | A4            |

| VCC    | GND     | 1 | 0    | 1 | 0 | 0 | 1 | 1 | 0 | A6            |

| OPEN   | VCC     | 1 | 0    | 1 | 0 | 1 | 0 | 0 | 0 | A8            |

| OPEN   | OPEN    | 1 | 0    | 1 | 0 | 1 | 0 | 1 | 0 | AA            |

| OPEN   | SDI     | 1 | 0    | 1 | 0 | 1 | 1 | 0 | 0 | AC            |

| OPEN   | GND     | 1 | 0    | 1 | 0 | 1 | 1 | 1 | 0 | AE            |

| SDI    | VCC     | 1 | 0    | 1 | 1 | 0 | 0 | 0 | 0 | B0            |

| SDI    | OPEN    | 1 | 0    | 1 | 1 | 0 | 0 | 1 | 0 | B2            |

| SDI    | SDI     | 1 | 0    | 1 | 1 | 0 | 1 | 0 | 0 | B4            |

| SDI    | GND     | 1 | 0    | 1 | 1 | 0 | 1 | 1 | 0 | B6            |

| GND    | VCC     | 1 | 0    | 1 | 1 | 1 | 0 | 0 | 0 | B8            |

| GND    | OPEN    | 1 | 0    | 1 | 1 | 1 | 0 | 1 | 0 | BA            |

| GND    | SDI     | 1 | 0    | 1 | 1 | 1 | 1 | 0 | 0 | BC            |

| GND    | GND     | 1 | 0    | 1 | 1 | 1 | 1 | 1 | 0 | BE            |

#### Table 9: Device Address Write Table and Configuration.

| Config | uration |   | Bits |   |   |   |   |   |   |               |

|--------|---------|---|------|---|---|---|---|---|---|---------------|

| ADDR1  | ADDR0   | 6 | 5    | 4 | 3 | 2 | 1 | 0 | R | Address (Hex) |

| VCC    | VCC     | 1 | 0    | 1 | 0 | 0 | 0 | 0 | 1 | A1            |

| VCC    | OPEN    | 1 | 0    | 1 | 0 | 0 | 0 | 1 | 1 | A3            |

| VCC    | SDI     | 1 | 0    | 1 | 0 | 0 | 1 | 0 | 1 | A5            |

| VCC    | GND     | 1 | 0    | 1 | 0 | 0 | 1 | 1 | 1 | A7            |

| OPEN   | VCC     | 1 | 0    | 1 | 0 | 1 | 0 | 0 | 1 | A9            |

| OPEN   | OPEN    | 1 | 0    | 1 | 0 | 1 | 0 | 1 | 1 | AB            |

| OPEN   | SDI     | 1 | 0    | 1 | 0 | 1 | 1 | 0 | 1 | AD            |

| OPEN   | GND     | 1 | 0    | 1 | 0 | 1 | 1 | 1 | 1 | AF            |

| SDI    | VCC     | 1 | 0    | 1 | 1 | 0 | 0 | 0 | 1 | B1            |

| SDI    | OPEN    | 1 | 0    | 1 | 1 | 0 | 0 | 1 | 1 | B3            |

| SDI    | SDI     | 1 | 0    | 1 | 1 | 0 | 1 | 0 | 1 | B5            |

| SDI    | GND     | 1 | 0    | 1 | 1 | 0 | 1 | 1 | 1 | B7            |

| GND    | VCC     | 1 | 0    | 1 | 1 | 1 | 0 | 0 | 1 | B9            |

| GND    | OPEN    | 1 | 0    | 1 | 1 | 1 | 0 | 1 | 1 | BB            |

| GND    | SDI     | 1 | 0    | 1 | 1 | 1 | 1 | 0 | 1 | BD            |

| GND    | GND     | 1 | 0    | 1 | 1 | 1 | 1 | 1 | 1 | BF            |

Table 10: Device Address Read Table and Configuration.

#### **Fault Reporting**

Each device possesses fault reporting registers and a fault flag. An open or short condition on each current sink is reported in one of four fault registers. An open fault condition is only monitored for LED current sink ontimes of greater than  $10\mu$ s. An over-temperature condition is reported in one of two registers. These conditions may selectively be reported on the open drain Fault pin. Bits in separate fault reporting registers can be set or reset to enable or disable a particular fault condition.

The shorted LED fault condition is handled in a special way because of the uncertainty associated with shorted LEDs and the LED forward voltage variation. To detect a shorted LED fault in the system, all LED channels should be programmed to be conducting for at least 1ms. The fault flag will only be valid 1ms after a given LED string has begun conducting. If the fault flag becomes active, the fault registers must be read while the channels remain conducting. The fault reporting register defaults to the condition of reporting the short detect, so this register must be cleared prior to checking for shorted LEDs. Severe LED forward voltage (V<sub>F</sub>) mismatches between channels will also be reported as a short fault condition.

#### **Fault Registers**

The fault registers can be read anytime during operation.

| ADD | R: E0h       |         | s Registe | ult1:<br>r Reports Fault<br>igh Voltage CS Pins |

|-----|--------------|---------|-----------|-------------------------------------------------|

| Bit | Bit<br>Name  | Default | Access    | Description                                     |

| 1:0 | CS1<br>Fault | 00h     | R         | 00: no fault, 01: open,<br>10: short            |

| 3:2 | CS2<br>Fault | 00h     | R         | 00: no fault, 01: open,<br>10: short            |

| 5:4 | CS3<br>Fault | 00h     | R         | 00: no fault, 01: open,<br>10: short            |

| 7:6 | CS4<br>Fault | 00h     | R         | 00: no fault, 01: open,<br>10: short            |

Table 11: Fault1 Register Settings.

### Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

|     | DDR:<br>E2h  | Fault2:<br>This Register Reports Fault<br>Conditions and High Voltage CS Pi |        |                                      |  |

|-----|--------------|-----------------------------------------------------------------------------|--------|--------------------------------------|--|

| Bit | Bit<br>Name  | Default                                                                     | Access | Description                          |  |

| 1:0 | CS5<br>Fault | 00h                                                                         | R      | 00: no fault, 01: open,<br>10: short |  |

| 3:2 | CS6<br>Fault | 00h                                                                         | R      | 00: no fault, 01: open,<br>10: short |  |

| 5:4 | CS7<br>Fault | 00h                                                                         | R      | 00: no fault, 01: open,<br>10: short |  |

| 7:6 | CS8<br>Fault | 00h                                                                         | R      | 00: no fault, 01: open,<br>10: short |  |

#### Table 12: Fault2 Register Settings.

|     | DDR:<br>E4h   | Fault3:<br>This Register Reports Fault<br>Conditions And High Voltage CS |        |                                      |

|-----|---------------|--------------------------------------------------------------------------|--------|--------------------------------------|

| Bit | Bit<br>Name   | Default                                                                  | Access | Description                          |

| 1:0 | CS9<br>Fault  | 00h                                                                      | R      | 00: no fault, 01: open,<br>10: short |

| 3:2 | CS10<br>Fault | 00h                                                                      | R      | 00: no fault, 01: open,<br>10: short |

| 5:4 | CS11<br>Fault | 00h                                                                      | R      | 00: no fault, 01: open,<br>10: short |

| 7:6 | CS12<br>Fault | 00h                                                                      | R      | 00: no fault, 01: open,<br>10: short |

#### Table 13: Fault3 Register Settings.

| ADE | DR: E6h       |         | s Registe | ult4:<br>r Reports Fault<br>igh Voltage CS Pins |

|-----|---------------|---------|-----------|-------------------------------------------------|

| Bit | Bit<br>Name   | Default | Access    | Description                                     |

| 1:0 | CS13<br>Fault | 00h     | R         | 00: no fault, 01: open,<br>10: short            |

| 3:2 | CS14<br>Fault | 00h     | R         | 00: no fault, 01: open,<br>10: short            |

| 5:4 | CS15<br>Fault | 00h     | R         | 00: no fault, 01: open,<br>10: short            |

| 7:6 | CS16<br>Fault | 00h     | R         | 00: no fault, 01: open,<br>10: short            |

Table 14: Fault4 Register Settings.

### **Temperature Fault Conditions**

Two thermal limits are reported in each AAT2400/2401 device. The first thermal limit serves as a warning that the device is heating up. When this condition is reported, the system can compensate by lowering the current levels of the current sinks. The second thermal limit is the maximum temperature allowed. When this temperature is reached, the control registers are reset to 0 which disables all current sinks. In addition, the boost converter in the master device is disabled. To resume operation, the control registers must be reset, and all of the configuration registers must be reprogrammed, since data retention at the maximum temperature is not guaranteed.

| ADDR:<br>E8h |             | OTMP1:<br>Reports the Temperature Conditio<br>of the Master IC (CS8 to CS1) |        |                                                                                                            |  |

|--------------|-------------|-----------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------|--|

| Bit          | Bit<br>Name | Default                                                                     | Access | Description                                                                                                |  |

| 1:0          | OTMP 1      | 00h                                                                         | R      | 00: Tj < T1<br>01: T1 < Tj < T2<br>11: T2 < Tj                                                             |  |

| 2            | Config      | 0h                                                                          | R/W    | 0: Report T1 and T2<br>Thermal Limits on<br>Fault pin<br>1: Report only T2 Ther-<br>mal Limit on Fault pin |  |

Table 15: OTMP1 Settings.

|     |             |         | the Tem | MP2:<br>operature Condition<br>C (CS16 to CS9)                                                             |

|-----|-------------|---------|---------|------------------------------------------------------------------------------------------------------------|

| Bit | Bit<br>Name | Default | Access  | Description                                                                                                |

| 1:0 | OTMP 2      | 00h     | R       | 00: Tj < T1<br>01: T1 < Tj < T2<br>11: T2 < Tj                                                             |

| 2   | Config      | 0h      | R/W     | 0: Report T1 and T2<br>Thermal Limits on<br>Fault pin<br>1: Report only T2 Ther-<br>mal Limit on Fault pin |

Table 16: OTMP2 Settings.

## Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

### **Fault Reporting Registers**

Each individual sink's fault reporting can be configured to the following cases: LED string becomes open, LED string becomes short completely, reporting both or report none. To turn this feature off, set two bits to '11'. Setting the two bits to '01' and '10' means reporting short condition only or reporting open condition only accordingly. To report both faulty conditions, set the two bits to '00'.

| A   | DDR: F0h  | Fault Reporting 1:<br>Individual Sink Fault Reportin |        |                                                                                            |  |

|-----|-----------|------------------------------------------------------|--------|--------------------------------------------------------------------------------------------|--|

| Bit | Bit Name  | Default                                              | Access | Description                                                                                |  |

| 1:0 | CS1 Fault | 10h                                                  | R/W    | 00: report both;<br>01: report short<br>only; 10: report<br>open only; 11:<br>report none. |  |

| 3:2 | CS2 Fault | 10h                                                  | R/W    | 00: report both;<br>01: report short<br>only; 10: report<br>open only; 11:<br>report none. |  |

| 5:4 | CS3 Fault | 10h                                                  | R/W    | 00: report both;<br>01: report short<br>only; 10: report<br>open only; 11:<br>report none. |  |

| 7:6 | CS4 Fault | 10h                                                  | R/W    | 00: report both;<br>01: report short<br>only; 10: report<br>open only; 11:<br>report none. |  |

#### Table 17: Fault Reporting Register 1 Settings.

| Sixteen-Channel White LED Driver Solution |

|-------------------------------------------|

| with Full LED Current and Timing Control  |

| A   | DDR: F2h  | Fault Reporting 2:<br>Individual Sink Fault Reporting |        |                                                                                            |  |  |

|-----|-----------|-------------------------------------------------------|--------|--------------------------------------------------------------------------------------------|--|--|

| Bit | Bit Name  | Default                                               | Access | Description                                                                                |  |  |

| 1:0 | CS5 Fault | 10h                                                   | R/W    | 00: report both;<br>01: report short<br>only; 10: report<br>open only; 11:<br>report none. |  |  |

| 3:2 | CS6 Fault | 10h                                                   | R/W    | 00: report both;<br>01: report short<br>only; 10: report<br>open only; 11:<br>report none. |  |  |

| 5:4 | CS7 Fault | 10h                                                   | R/W    | 00: report both;<br>01: report short<br>only; 10: report<br>open only; 11:<br>report none. |  |  |

| 7:6 | CS8 Fault | 10h                                                   | R/W    | 00: report both;<br>01: report short<br>only; 10: report<br>open only; 11:<br>report none. |  |  |

#### Table 18: Fault Reporting Register 2 Settings.

| A   | DDR: F4h   | Fault Reporting 3:<br>Individual Sink Fault Reporting |        |                                                                                            |  |  |

|-----|------------|-------------------------------------------------------|--------|--------------------------------------------------------------------------------------------|--|--|

| Bit | Bit Name   | Default                                               | Access | Description                                                                                |  |  |

| 1:0 | CS9 Fault  | 10h                                                   | R/W    | 00: report both;<br>01: report short<br>only; 10: report<br>open only; 11:<br>report none. |  |  |

| 3:2 | CS10 Fault | 10h                                                   | R/W    | 00: report both;<br>01: report short<br>only; 10: report<br>open only; 11:<br>report none. |  |  |

| 5:4 | CS11 Fault | 10h                                                   | R/W    | 00: report both;<br>01: report short<br>only; 10: report<br>open only; 11:<br>report none. |  |  |

| 7:6 | CS12 Fault | 10h                                                   | R/W    | 00: report both;<br>01: report short<br>only; 10: report<br>open only; 11:<br>report none. |  |  |

#### Table 19: Fault Reporting Register 3 Settings.

| A   | DDR: F6h   | Fault Reporting 4:<br>Individual Sink Fault Reporting |        |                                                                                            |  |  |

|-----|------------|-------------------------------------------------------|--------|--------------------------------------------------------------------------------------------|--|--|

| Bit | Bit Name   | Default                                               | Access | Description                                                                                |  |  |

| 1:0 | CS13 Fault | 10h                                                   | R/W    | 00: report both;<br>01: report short<br>only; 10: report<br>open only; 11:<br>report none. |  |  |

| 3:2 | CS14 Fault | 10h                                                   | R/W    | 00: report both;<br>01: report short<br>only; 10: report<br>open only; 11:<br>report none. |  |  |

| 5:4 | CS15 Fault | 10h                                                   | R/W    | 00: report both;<br>01: report short<br>only; 10: report<br>open only; 11:<br>report none. |  |  |

| 7:6 | CS16 Fault | 10h                                                   | R/W    | 00: report both;<br>01: report short<br>only; 10: report<br>open only; 11:<br>report none. |  |  |

#### Table 20: Fault Reporting Register 4 Settings.

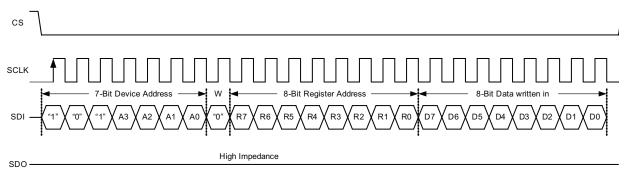

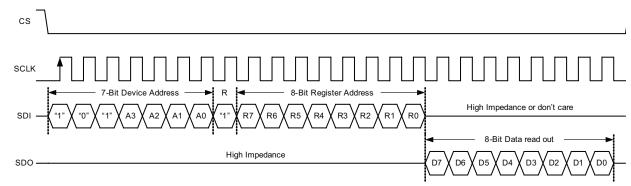

### Serial Peripheral Interface (SPI)

The serial peripheral interface is a synchronous serial interface for address and data transfer at bit rates of up to 30Mhz. It is configured in 8-bit bytes designed to interface with a standard SPI bus on many microcontrollers. Four pins are used to communicate on the SPI: SCLK (synchronous clock), CS (chip select, to signify the start of a transfer), SDI (data input to the AAT2400/2401 for write operations, latched on the rising edge of SCLK), and SDO (data output from the AAT2400/2401 for read operations, presented on the falling edge of SCLK).

Data and address are always sent MSB first. The first 8-bit byte of a transfer is always the device address. The second byte of a transfer is always the address of the register to be written to or read from. The subsequent bytes are one or more bytes of data. The LSB (bit 0) of the device address byte contains a bit that signifies a read or a write operation. If R/W is 0, one or more write cycles occur, and if R/W is 1, one or more read cycles occur.

Multi-byte transfers are similar to single byte transfers, except that the CS pin is held low, and additional SCLK cycles are sent until the end of the burst. In multi-byte transfers, the registers are written to or read from in sequential order. After the end of the address space, the multi-byte transfer is terminated.

## Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

#### **SPI Single-Byte Write**

#### SPI Single-Byte Read

#### SPI Multi-Byte Write Transfer

#### SPI Multi-Byte Read Transfer

Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com 202307A • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice. • August 24, 2012

## **Application Information**

### **Channel Disable**

If current sink channels on either the AAT2400 or AAT2401 are not used, they must be terminated. Unused channels should have their corresponding bit in the CTL1 or CTL2 register set to zero. In applications where the AAT2400/AAT2401 pair are used, unused channels may be tied to GND or to VCC. In applications where the AAT2401 is used alone, unused channels must be tied to VCC.

### **LED Selection**

Although the AAT2400 and 2401 are specifically designed to drive high current white LEDs, the device can also be used to drive most types of LEDs with forward voltages ranging between 2.0V and 4.7V. Since all current sinks are matched with low voltage dependence, the LED-to-LED brightness will be matched regardless of the individual LED forward voltage ( $V_F$ ) levels. It makes the AAT2400 and 2401 a perfect combination for large LCD TV backlighting LED applications.

#### **Constant Current Setting**

The LED current is controlled by the  $R_{\text{SET}}$  resistor. For maximum accuracy, a 1% tolerance resistor is recommended. Table 21 shows the  $R_{\text{SET}}$  resistor value for AAT2400 and 2401 for various LED full-scale current levels.

$$R_{SET} = \frac{1024(A/A) \cdot 0.6V}{I_{CSY}}$$

| I <sub>csx</sub> (mA) | R <sub>set</sub> (kΩ) |

|-----------------------|-----------------------|

| 40                    | 15.4                  |

| 50                    | 12.3                  |

| 60                    | 10.2                  |

| 70                    | 8.76                  |

| 80                    | 7.68                  |

| 90                    | 6.81                  |

| 100                   | 6.12                  |

Table 21: Maximum LED Current and R<sub>SET</sub>Resistor Values (1% Resistor Tolerance).

### **Over-Voltage Protection**

The over-voltage protection circuit consists of a resistor network connected from the output voltage to the OVP pin (see Figure 2). This over voltage protection circuit

### Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

prevents damage to the device when one of the 16 channels has an open LED circuit. The rest of the channels of AAT2400 and AAT2401 continue to operate.

The resistor divider can be selected such that the overvoltage threshold occurs prior to the output reaching 45V (V<sub>OUT(MAX)</sub>). The value of R5 should be selected from 10k $\Omega$ to 20k $\Omega$  to minimize switching losses without degrading noise immunity.

$R_4 = R_5 \left( \frac{V_{OUT(PROTECTION)}}{V_{OVD}} - 1 \right)$

Figure 2: Over-Voltage Protection Circuit.

If 10 LEDs are connected in series on one channel sink, the total V<sub>F</sub> from the WLEDs could be as high as 42V. Therefore, using R5 = 12.1k $\Omega$  and setting V<sub>OUT(PROTECTION)</sub> = 45V is recommended. Selecting a 1% resistor, this results in R4 = 442k $\Omega$  (rounded to the nearest standard 1% value). It is always recommended to use the same number of WLEDs on each channel and set the appropriate over-voltage protection. Failure to do so may cause any one of the 16 sink pins to exceed the absolute maximum rating voltage and permanently damage the device in case the channel is disconnected (open circuit failure).

### **LED Brightness Control**

The AAT2400 and 2401 uses the SPI interface to program and control LED brightness. Each channel sink current of the AAT2400 and AAT2401 can be changed successively to brighten or dim the LED string in smooth transitions (i.e. dynamic local dimming or zone dimming), giving the user complete programmability and real-time control of LED brightness to tune the picture background to a trueblack and a true-white from the LED technology.

#### Minimum and Maximum Practical Settings for Gray Scale and Delay Registers

When using the internally generated PLL derived PWM timebase, the stability of the frequency on  $V_{SYNC}$  defines the practical minimum and maximum settings for the gray scale and delay registers. As a rule, the minimum and maximum settings should be 4 counts away from full scale. In other words, the register settings should lie between 04h and 0FFBh. Otherwise, the natural phase delay between jitter on  $V_{SYNC}$  and the internal timebase may result in unexpected PWM timing. Gray scale set to zero, however, always results in zero on time.

### Selecting the Schottky Diode

To ensure minimum forward voltage drop and no recovery, high voltage Schottky diodes are recommended for the AAT2400 boost converter. The output diode is selected to maintain acceptable efficiency and reasonable operating junction temperature under full load operating conditions. Forward voltage (V<sub>F</sub>) and package thermal resistance ( $\theta_{JA}$ ) are the dominant factors in selecting a diode. The diode non-repetitive peak forward surge current rating ( $I_{FSM}$ ) should be considered for high pulsed load applications. I<sub>FSM</sub> rating drops with increasing conduction period.

Manufacturers' datasheets should be reviewed carefully to verify reliability under peak loading conditions. The diode's published current rating may not reflect actual operating conditions and should be used only as a comparative measure between similarly rated devices.

60V/3A rated Schottky diodes are recommended for output voltages less than 45V (total  $V_{\rm F}$  and 100mA/sink application).

#### Estimating Schottky Diode Power Dissipation

The switching period is divided between ON and OFF time intervals:

$$\frac{1}{F_{s}} = t_{on} + t_{off} = D + D'$$

During the ON time, the N-channel power MOSFET is conducting and storing energy in the boost inductor. During the OFF time, the N-channel power MOSFET is

## Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

not conducting. Stored energy is transferred from the input battery and boost inductor to the output load through the output diode.

Duty cycle is defined as the ON time divided by the total switching interval:

$$\mathsf{D} = \frac{\mathsf{t}_{\mathsf{ON}}}{\mathsf{t}_{\mathsf{ON}} + \mathsf{t}_{\mathsf{OFF}}} = \mathsf{t}_{\mathsf{ON}} \cdot \mathsf{F}_{\mathsf{S}}$$

The maximum duty cycle can be estimated from the relationship for a continuous mode boost converter. Maximum duty cycle ( $D_{MAX}$ ) is the duty cycle at minimum input voltage ( $V_{IN(MIN)}$ ):

$$\mathsf{D}_{\mathsf{MAX}} = \frac{\mathsf{V}_{\mathsf{OUT}} - \mathsf{V}_{\mathsf{IN}(\mathsf{MIN})}}{\mathsf{V}_{\mathsf{OUT}}}$$

The average diode current during the OFF time can be estimated:

$$I_{AVG(OFF)} = \frac{I_{OUT}}{1 - D_{MAX}}$$

The  $V_{\scriptscriptstyle F}$  of the Schottky diode can be estimated from the average current during the off time. The average diode current is equal to the output current:

$$I_{AVG(TOT)} = I_{OUT}$$

The average output current multiplied by the forward diode voltage determines the loss of the output diode:

$$\mathsf{P}_{\mathsf{LOSS}(\mathsf{DIODE})} = \mathsf{I}_{\mathsf{AVG}(\mathsf{TOT})} \cdot \mathsf{V}_{\mathsf{F}} = \mathsf{I}_{\mathsf{OUT}} \cdot \mathsf{V}_{\mathsf{F}}$$

For continuous LED currents, the diode junction temperature can then be estimated:

$$\Gamma_{J(DIODE)} = T_{AMB} + \Theta_{JA} \cdot P_{LOSS(DIODE)}$$

External Schottky diode junction temperature should be below 110°C, and may vary depending on application and/or system guidelines. The diode  $\theta_{JA}$  can be minimized with additional metal PCB area on the cathode. However, adding additional heat-sinking metal around the anode may degrade EMI performance. The reverse leakage current of the rectifier must be considered to maintain low quiescent (input) current and high efficiency under light load. The rectifier reverse current increases dramatically at elevated temperatures.

## Sixteen-Channel White LED Driver Solution with Full LED Current and Timing Control

| Manufacturer | Part Number | Rated Foward<br>Current (A) | Rated Voltage<br>(V) | Thermal Resistance,<br>θ <sub>JA</sub> , (°C/W) | Case |

|--------------|-------------|-----------------------------|----------------------|-------------------------------------------------|------|

| Diode, Inc.  | B360A       | 3A                          | 60                   | 100                                             | SMA  |

| ON Semi      | MBRD360     | 3A                          | 60                   | 80                                              | DPAK |

Table 22: Typical Surface Mount Schottky Rectifiers for Various Output Loads(select T<sub>1</sub> < 110°C in Application Circuit).</td>

#### **Selecting the Boost Inductor**

The AAT2400 controller utilizes PWM control and the switching frequency is fixed. To maintain 600kHz switching frequency and stable operation, a  $10\mu$ H inductor is recommended. Manufacturer's specifications list both the inductor DC current rating, which is a thermal limitation, and peak inductor current rating, which is determined by the saturation characteristics. Measurements at full load and high ambient temperature should be performed to ensure that the inductor does not saturate or exhibit excessive temperature rise.

The output inductor (L) is selected to avoid saturation at minimum input voltage and maximum output load conditions. Worst-case peak current occurs at minimum input voltage (maximum duty cycle) and maximum load. At high load the switching frequency is somewhat diminished, resulting in higher  $I_{PEAK}$ . Bench measurements are recommended to confirm actual  $I_{PEAK}$  and to ensure that

the inductor does not saturate at maximum LED current and minimum input supply voltage. The RMS current flowing through the boost inductor is equal to the DC plus AC ripple components. Under worst case RMS conditions, the current waveform is critically continuous. The resulting RMS calculation yields worst case inductor loss. The RMS current value should be compared against the inductor manufacturer's temperature rise, or thermal degrading, guidelines:

$$I_{\text{RMS}} = \frac{I_{\text{PEAK}}}{\sqrt{3}}$$

For a given inductor type, smaller inductor size leads to an increase in DCR winding resistance and, in most cases, increased thermal impedance. Winding resistance degrades boost converter efficiency and increases the inductor's operating temperature:

$$P_{LOSS(L)} = I^2_{RMS} \cdot DCR$$

| Manufacturer       | Part Number           | Inductance<br>(µH) | Saturated<br>Rated Current<br>(A) | DCR<br>(mΩ) | Size (mm)<br>LxWxH | Туре               |

|--------------------|-----------------------|--------------------|-----------------------------------|-------------|--------------------|--------------------|

| Cooper<br>Bussmann | DR1040-100-R          | 10                 | 4.4                               | 26          | 10.3 x 10.5 x 4.0  | Shielded Drum Core |

| Cooper<br>Bussmann | DR1050-100-R          | 10                 | 4.58                              | 18          | 10.3 x 10.5 x 5.0  | Shielded Drum Core |

| Sumida             | CDR12D43RNP-100M      | 10                 | 6.3                               | 18          | 12.4 x 12.4 x 4.5  | Shielded Drum Core |

| Sumida             | CDR10D48MNNP-100MC    | 10                 | 5.5                               | 32          | 10.3 x 10.3 x 5.0  | Shielded Drum Core |

| Sumida             | CDRH10D43RNP-100NC    | 10                 | 5.2                               | 26.1        | 10.5 x 10.8 x 4.5  | Shielded Drum Core |

| Sumida             | CDRH105RNP-100NC      | 10                 | 4.45                              | 26          | 10.3 x 10.5 x 5.0  | Shielded Drum Core |

| TDK                | VLF10045T-100M4R3-PF  | 10                 | 4.3                               | 25          | 9.7 x 10.0 x 4.5   | Shielded Drum Core |

| TDK                | RLF12545T-100M5R1-PF  | 10                 | 6                                 | 12.4        | 12.8 x 12.5 x 4.7  | Shielded Drum Core |

| Würth Elektronik   | WE-PD Type "LS" - 100 | 10                 | 4.2                               | 25          | 12 x 12 x 4.5      | Shielded Drum Core |